October 2004

RMDA20420

# FAIRCHILD

SEMICONDUCTOR®

# RMDA20420 20–42 GHz Broadband Driver Amplifier

#### **General Description**

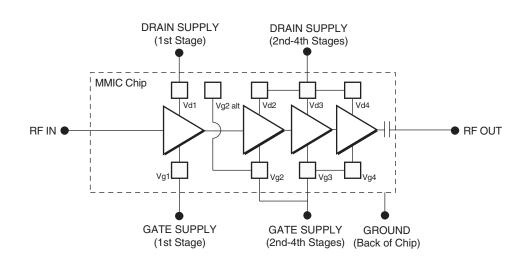

The Fairchild Semiconductor's RMDA20420 is a broadband driver amplifier designed for use in point to point radio, point to multi-point communications, LMDS, SatCom and various communication applications. The RMDA20420 is a fully matched GaAs MMIC utilizing our advanced 0.15µm gate length PHEMT process.

#### Features

- Wideband 20–42GHz operation

- 22dB small signal gain (typ.)

- 23dBm saturated power output (typ.)

- Matched to  $50\Omega$

- Optional bonding configuration for multiplier applications

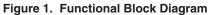

- Chip Size 1.720mm x 0.760mm

Device

## **Absolute Ratings**

| Symbol           | Parameter                                | Ratings     | Units |

|------------------|------------------------------------------|-------------|-------|

| Vd               | Positive DC Voltage (+3.5V Typical)      | +5          | V     |

| Vg               | Negative DC Voltage                      | -2          | V     |

| Vdg              | Simultaneous (Vd - Vg)                   | +7          | V     |

| ld               | Positive DC Current                      | 600         | mA    |

| Pin              | RF Input Power (from 50 $\Omega$ source) | 15          | dBm   |

| Тс               | Operating Baseplate Temperature          | -40 to +85  | °C    |

| T <sub>STG</sub> | Storage Temperature Range                | -55 to +125 | °C    |

| R <sub>JC</sub>  | Thermal Resistance (Channel to Backside) | 57          | °C/W  |

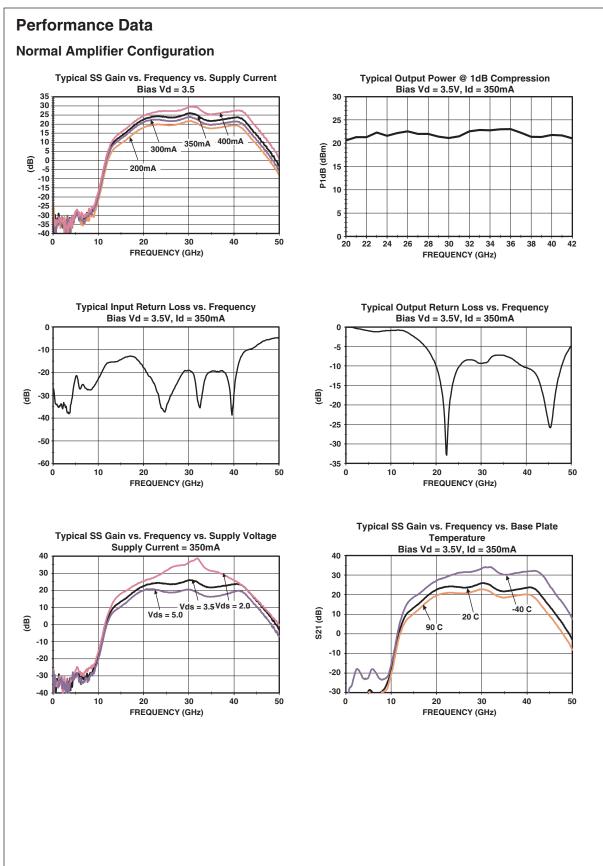

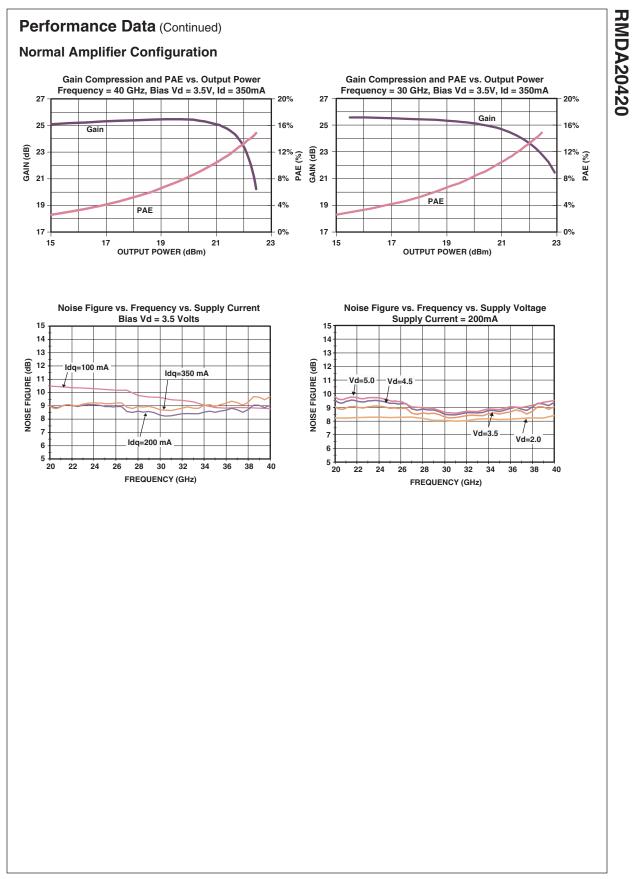

## **Electrical Characteristics**<sup>1</sup>

| Parameter                                        | Min | Тур        | Max   | Units    |

|--------------------------------------------------|-----|------------|-------|----------|

| Frequency Range                                  | 20  |            | 42    | GHz      |

| Drain Supply Voltage (Vd)                        | 2   | 3.5        | 5     | V        |

| Gate Supply Voltage (Vg) <sup>2</sup>            | -2  | -0.6       | -0.15 | V        |

| Small Signal Gain <sup>3</sup><br>(f = 20-22GHz) | 18  | 20         |       | dB       |

| (f = 22-42GHz)<br>Gain Variation vs.Frequency    | 20  | 22<br>±2.5 |       | dB<br>dB |

| Power Output at 1dB Compression                  |     | 21         |       | dBm      |

| Power Output Saturated <sup>4</sup>              | 22  | 23         |       | dBm      |

| Drain Current at P1dB Compression                |     | 355        |       | mA       |

| Drain Current at Psat                            |     | 362        |       | mA       |

| Input Return Loss<br>(Pin = -20dBm)              |     | 12         |       | dB       |

| Output Return Loss<br>(Pin = -20dBm)             |     | 10         |       | dB       |

Notes:

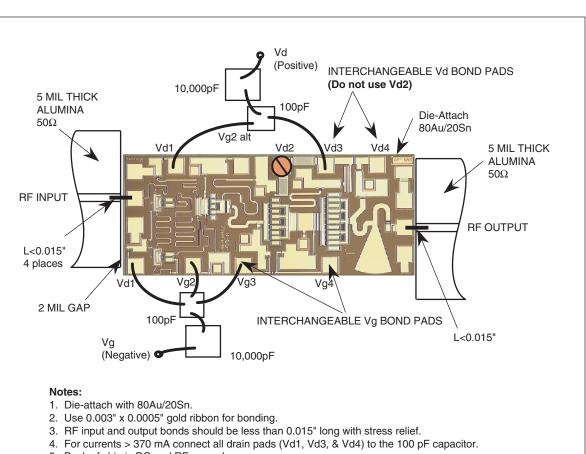

Notes: 1. Operated at 25°C, 50Ω system, Vd = +3.5V, quiescent current (Idq) = 350mA. 2. Typical range of the negative gate voltage is -0.9 to -0.15V to set typical Idq of 350mA. 3. Production measurements for small signal gain are made over a frequency range of 20 to 40GHz. 4. Saturated power measurements are not 100% tested, but guaranteed by design.

- 5. Back of chip is DC and RF ground.

- 6. Do not use Vd2 pad for drain bias connection.

#### Figure 4. Recommended Assembly and Bonding Diagram

### **Recommended Procedure (for biasing and operation)**

CAUTION: LOSS OF GATE VOLTAGE (Vg) WHILE DRAIN VOLTAGE (Vd) IS PRESENT CAN DAMAGE THE AMPLIFIER.

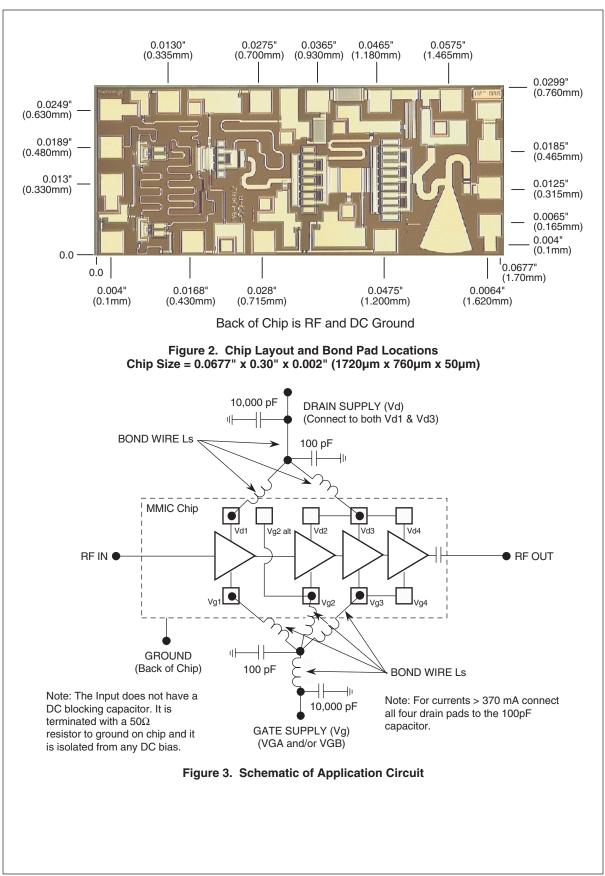

The following sequence must be followed to properly test the amplifier:

Step 1: Turn off RF input power.

**Step 2:** Connect the DC supply grounds to the ground of the chip carrier. Slowly apply negative gate bias supply voltage of -1.5V to Vg.

Step 3: Slowly apply positive drain bias supply voltage of +3.5V to Vd.

**Step 4:** Adjust gate bias voltage to set the quiescent current of Idq = 350 mA.

**Step 5:** After the bias condition is established, the RF input signal may now be applied at the appropriate frequency band.

Step 6: Follow turn-off sequence of:

- (i) Turn off RF input power,

- (ii) Turn down and off drain voltage (Vd),

- (iii) Turn down and off gate bias voltage (Vg).

**RMDA20420**

## **Application Information**

#### CAUTION: THIS IS AN ESD SENSITIVE DEVICE

Chip carrier material should be selected to have GaAs compatible thermal coefficient of expansion and high thermal conductivity such as copper molybdenum or copper tungsten. The chip carrier should be machined, finished flat, plated with gold over nickel and should be capable of withstanding 325°C for 15 minutes.

Die attachment for power devices should utilize Gold/Tin (80/20) eutectic alloy solder and should avoid hydrogen environment for PHEMT devices. Note that the backside of the chip is gold plated and is used as RF and DC Ground.

These GaAs devices should be handled with care and stored in dry nitrogen environment to prevent contamination of bonding surfaces. These are ESD sensitive devices and should be handled with appropriate precaution including the use of wrist-grounding straps. All die attach and wire/ribbon bond equipment must be well grounded to prevent static discharges through the device.

Recommended wire bonding uses 3 mils wide and 0.5 mil thick gold ribbon with lengths as short as practical allowing for appropriate stress relief. The RF input and output bonds should be typically 0.012" long corresponding to a typical 2 mil gap between the chip and the substrate material.

**RMDA20420**

# RMDA20420

## **Application Information**

The RMDA20420 can be used as an even harmonic multiplier or as an odd harmonic multiplier depending on the type of DC biasing arrangement being used. Optimum DC bias is applied to peak the desired harmonic which falls into the 20 to 42GHz passband. The following application information will detail the configuration and procedure for using the RMDA20420 as an even harmonic multiplier and as an odd harmonic multiplier. Typical measured data is provided at selected frequencies within the passband with the RMDA20420 configured as a doubler and as a tripler.

#### **Multiplier Operation**

The RMDA20420 is a four stage general purpose MMIC amplifier covering the 20-42GHz passband. The amplifier has a steep gain roll off at the band edges and the input return loss of the amplifier is better than 10dB from 42GHz down to DC. Any multiplier harmonics, which fall in the passband, will get amplified and any harmonics that fall below the passband will get suppressed.

A deliberate design feature that makes the RMDA20420 an effective multiplier is the ability to independently bias the first stage. This feature allows freedom to determine the optimum DC bias condition required to peak the desired harmonic and suppressing the unwanted harmonics. Optimum DC bias conditions depend largely on factors such as fundamental frequency, desired harmonic frequency, input power level, output power level and suppression requirements.

### Test Set Up

The basic test set uses a source to provide the input signal at the desired frequency and power level. The DUT was biased either as an even harmonic or odd harmonic operation and the output was observed on a spectrum analyzer. The power of the harmonics was measured using the spectrum analyzer with all the cable losses accounted. Figure 5 shows the basic test set used.

Figure 5. Basic Test Set Up

### **Even Harmonic Operation**

Even harmonics are generated whenever the symmetry of the input signal waveform is distorted. This is accomplished by biasing the first stage operating point in a region of the I-V curve where the device is near pinch-off. In this condition, the first stage becomes a half wave rectifier where conduction only occurs on positive half cycles of the input waveform. Thus, presenting an asymmetrical waveform consisting mainly of positive half cycles which is rich in even harmonics to the remaining stages of the amplifier.

For most even harmonic multiplier operations, the first stage is usually pinched off and the remaining stages are biased as a linear amplifier. As an example, the RMDA20420 was evaluated as a doubler.

In the doubler operation, two drain voltages of +3.5V were used: One for first stage (Vd1) and the other (Vd2) for the remaining 3 stages tied together as shown in Figure 6. Independent biasing of the first stage was achieved by using two separate gate voltages. Vg1 was used for stage one and set to Vg1 = -1.0V (near pinch-off). Vg2 was used for the remaining three stages. Vg2 was adjusted until Idq = 330mA.

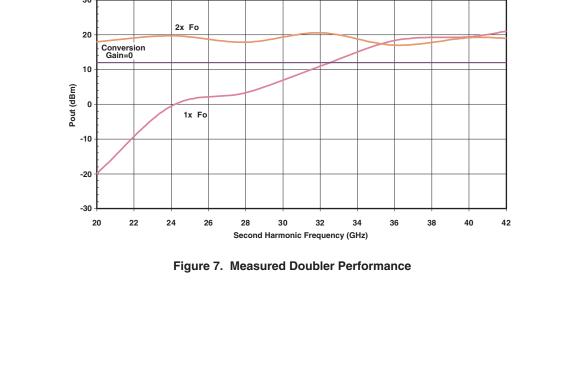

Vd1 Vd2 Vd2 Vd3 Vg2 alt Vd4 Vd1 RF IN RF OUT Vg /g2 Vg3 Vg2 Vg1 Figure 6. RMDA20420 Configured as Doubler For each input frequency and input power level, Vg1 was adjusted to peak the second harmonic. Small changes in Vg2 and Vd2 at this point help in suppressing odd harmonics. Figure 7 shows the doubler performance over the 20 to 42GHz band for a fixed input power level of +12dBm. The graph shows doubled frequencies with output power levels greater than +16dBm over the 20-42GHz band. The graph also shows the increasing power level of the fundamental at the higher end of the band since the fundamental frequency approaches the lower band edge of the amplifier passband. Based on these measurements the RMDA20420 can be used a doubler to give desired frequencies anywhere in the 20-42GHz band with a conversion gain up to 8dB and second harmonic power levels up to 20dBm. 30 2x Fo 20 Conversion Gain=0 10

**RMDA20420**

# **RMDA20420**

#### **Odd Harmonic Operation**

Odd harmonics are generally associated with a square wave. The RMDA20420 is biased in such a way that causes the clipping of the input sine wave to closely approximate a square wave provided a high input drive level is maintained. If biased in a manner, which causes the input waveform to be clipped equally in the positive and negative cycles, then a symmetrical square wave will be approximated which contains odd harmonics.

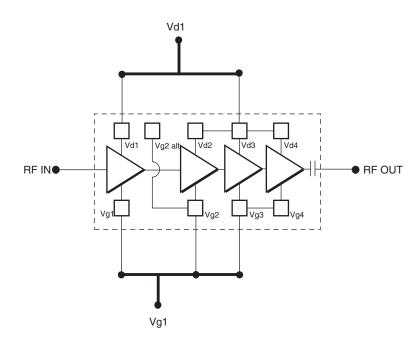

As an example, the RMDA20420 was biased as a tripler over the 20-40GHz band at selected frequencies. In this mode of operation all the drains voltages (Vd1 and Vd2) were tied together and all the gate voltages were tied together as shown in Figure 8.

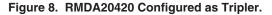

The test set up for this mode of operation is as shown in Figure 5. The biasing procedure requires the gate voltage Vg1 to be initially set to -1.0V. Next the drain voltage Vd1 was set to +2.0V. The input frequency was selected to give the desired tripled output and the input drive level was set to +14dBm. The output of the RDMA20420 was observed and the harmonics of the input frequency were visible on the spectrum analyzer display. The gate voltage Vg1 was adjusted gradually to peak the third harmonic. Lowering Vg1 resulted in peaking the third harmonic. Then the drain voltage Vd1 was adjusted to tweak the power level of the third harmonic. Tweaking Vg1 and Vd1 at this point resulted in further optimization of the desired harmonic or suppression of the unwanted harmonic as required. The range for Vg1 was between -0.1 to -0.6V and the range for Vd1 was between +1.1 to +1.8V. The above procedure was repeated for each input frequency tested.

Figure 9 shows the tripled output for the RMDA20420 biased as described above. Input frequencies were selected to give tripled frequencies falling in the 21 to 39GHz band. The graph shows tripled output powers greater than +10dBm up to 39GHz. The power levels of the first and second harmonics were also plotted to show the level of suppression of the unwanted harmonics. The graph shows for a tripled frequency of 30GHz the output power was +14dBm, the fundamental (10GHz) power level was -17dBm and the second harmonic (20GHz) power level was +3 dBm. The conversion gain for the tripled output at 30GHz was 0dB. For tripled frequencies between 21 to 39GHz, the conversion gain was better than -4dB.

©2004 Fairchild Semiconductor Corporation

#### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

| ACEx™                                                                                                  | FAST®                          | ISOPLANAR™                     | Power247™                                            | Stealth™                 |

|--------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|------------------------------------------------------|--------------------------|

| ActiveArray™                                                                                           | FASTr™                         | LittleFET™                     | PowerEdge™                                           | SuperFET™                |

| Bottomless™                                                                                            | FPS™                           | MICROCOUPLER™                  | PowerSaver™                                          | SuperSOT™-3              |

| CoolFET™                                                                                               | FRFET™                         | MicroFET™                      | PowerTrench <sup>®</sup>                             | SuperSOT <sup>™</sup> -6 |

| CROSSVOLT™                                                                                             | GlobalOptoisolator™            | MicroPak™                      | QFET <sup>®</sup>                                    | SuperSOT <sup>™</sup> -8 |

| DOME™                                                                                                  | GTO™່                          | MICROWIRE™                     | QS™                                                  | SyncFET™                 |

| EcoSPARK™                                                                                              | HiSeC™                         | MSX™                           | QT Optoelectronics <sup>™</sup>                      | TinyLogic <sup>®</sup>   |

| E <sup>2</sup> CMOS™                                                                                   | I²C™                           | MSXPro™                        | Quiet Series <sup>™</sup>                            | TINYOPTO™                |

| EnSigna™                                                                                               | <i>i-Lo</i> ™                  | OCX™                           | RapidConfigure™                                      | TruTranslation™          |

| FACT™                                                                                                  | ImpliedDisconnect <sup>™</sup> | OCXPro™                        | RapidConnect™                                        | UHC™                     |

| FACT Quiet Serie                                                                                       |                                | OPTOLOGIC <sup>®</sup>         | µSerDes™                                             | UltraFET <sup>®</sup>    |

| Across the board. Around the world.™<br>The Power Franchise <sup>®</sup><br>Programmable Active Droop™ |                                | OPTOPLANAR™<br>PACMAN™<br>POP™ | SILENT SWITCHER <sup>®</sup><br>SMART START™<br>SPM™ | VCX™                     |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

#### **Definition of Terms**

| Formative or      |                                                                                                                                                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In Design         | This datasheet contains the design specifications for<br>product development. Specifications may change in<br>any manner without notice.                                                                                          |

| First Production  | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| Full Production   | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Not In Production | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |

|                   | Full Production                                                                                                                                                                                                                   |